## UNIVERSITY OF ESWATINI FACULTY OF SCIENCE AND ENGINEERING DEPARTMENT OF PHYSICS

## MAIN EXAMINATION, DECEMBER 2018

TITLE OF PAPER

: ELECTRONICS 1

COURSE NUMBER : PHY 311

TIME ALLOWED

THREE HOURS

INSTRUCTIONS

: Answer FOUR (4) questions only.

: Each Question carries 25 Marks

Marks for different Sections are shown

in far Right margin.

THIS PAPER HAS 6 PAGES, INCLUDING THIS ONE.

DO NOT OPEN THE PAPER UNTIL PERMISSION IS GRANTED BY THE INVIGILATOR.

- 1. (a) Define the following

- (i) Intrinsic semiconductor [1]

- (ii) Doping [1]

- (iii) pn-junction. [1]

- (b) Sketch a bridge rectifier and the output (without a smoothening capacitor) and explain how it works. [5]

- (c) Assume that a smoothening capacitor C was connected across the load resistor of the bridge rectifier. With the aid of a schematic diagram of the variation of the output signal with time, show that the ripple voltage,  $V_r$  can be written as [7]

$$V_r = \frac{I_{av}}{2fC},$$

where  $I_{av}$  is the d.c. current and f is the frequency.

- (d) Modify the bridge circuit in (b) above to obtain a voltage doubler circuit and sketch the output signal if the input is sinusoidal. [4]

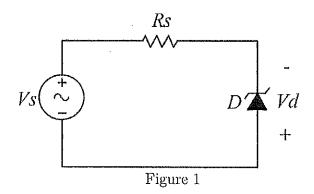

- (e) Consider the circuit in Figure 1.

- (i) Using the Zener diode model, obtain the load line equation for the circuit. [4]

- (ii) Sketch the I-V characteristics of the diode together with the load line. [2]

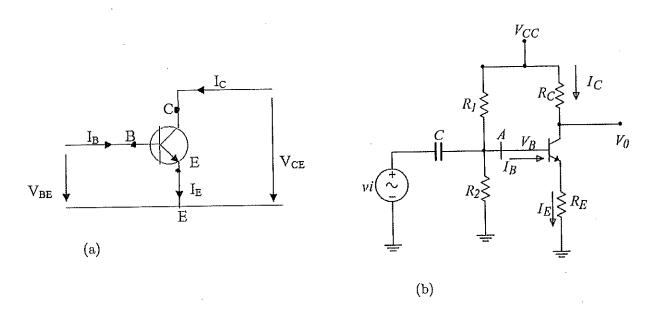

2. (a) With reference to Figure 2a, calculate the current gains  $\alpha$  and  $\beta$  when  $I_B=14.46~\mu A$  and  $I_E=1.46~m A$ . The base-emitter voltage is 0.7 V. [4]

(b) The table below shows the results of some dc measurements performed in the circuit of a npn BJT.

| Fixed $V_{CE1}$ |            | Fixed $V_{CE2}$ |               |

|-----------------|------------|-----------------|---------------|

| $I_B (\mu A)$   | $I_C (mA)$ | $V_{BE}(V)$     | $I_B (\mu A)$ |

| 100             | 9          | 0.65            | 100           |

| 120             | 11.2       | 0.66            | 150           |

(i) Determine approximate value of  $\beta$  with respect to the operating point. [3]

[3]

- (ii) Find the value of  $h_{ie}$  at the operating point.

- (c) For the circuit in Figure 2b,  $V_{CC}=15V$ ,  $R_C=5.1~k\Omega$ ,  $R_E=3.9~k\Omega$ ,  $R_1=10~k\Omega$  and  $R_2=4.7~k\Omega$ .

- (i) Determine the values of  $I_E$ ,  $I_C$ ,  $V_{RC}$ ,  $V_{RE}$  and  $V_{CE}$ . [10]

- (ii) If the minimum value of  $\beta$  is 50, find the maximum possible value of  $I_B$ . Assume  $V_{BE}=0.7V$ . [2]

- (iii) Determine the input resistance  $r_{be}$  of the transistor. [3]

- 3. (a) With the aid of a diagram(s) and characteristics, discuss the principle of operation of the n-channel JFET. [12]

- (b) Write the equation relating the drain current,  $I_D$  in terms of  $V_{GS}$  of an n-channel JFET. [3]

- (c) Sketch the small signal equivalent circuit of a common-source amplifier in terms of a current dependent voltage source. [3]

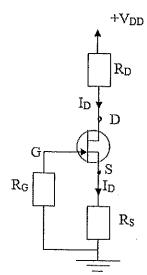

- (d) An n-channel JFET with a saturation current  $I_{DSS} = 6mA$  and pinch-off voltage  $V_P = -6V$  is used in the self-bias circuit of Figure 3. Given that  $V_{DD} = 12V$ ,  $R_D = 1.5 \text{ k}\Omega$  and  $R_S = 500\Omega$ , determine the operating point  $(I_D, V_{DS} \text{ and } V_{GS})$ .

Figure 3: Self-bias circuit of a JFET

- 4. (a) Draw the circuit diagram of a constant current source using a junction FET. [3]

- (b) Show that the internal resistance of the current source may be expressed as [7]

$$R_i \simeq \mu \left(1 - \sqrt{\frac{I_D}{I_{DSS}}}\right) \frac{|V_P|}{I_D}.$$

- (c) In a JFET source follower, the FET has a transconductance  $g_m = 15 \ m\Omega^{-1}$ . The source resistor  $R_S = 5 \ k\Omega$ . Find the voltage gain  $A_v$  and the output resistance  $R_o$ .

- (d) Using schematic diagrams, mention the difference between the depletion-mode and enhancement-mode MOSFETs. [5]

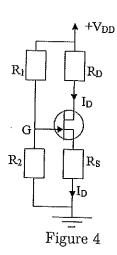

- (e) The biasing circuit in Figure 4 has the following circuit values:  $V_{DD}=18V,\ R_1=300\ \mathrm{k}\Omega,\ R_2=150\ \mathrm{k}\Omega,\ R_D=500\ \Omega$  and  $R_S=4\ \mathrm{k}\Omega$ . If the n-channel JFET has  $I_{DSS}=8mA$  and  $V_P=-4V$ , determine the operating point.

- 5. (a) Draw the small-signal equivalent circuit diagram of a common collector amplifier. [3]

- (b) Show that the voltage gain is expressed as [9]

$$A_v = \frac{\beta + 1}{\beta + 1 + \frac{r_{be}}{R_E} + \frac{r_{be}}{r_{ce}}}$$

- (c) Simplify  $A_v$  when  $r_{be} \ll \beta R_E$  and  $r_{be} \ll \beta r_{ce}$ . [3]

- (d) Given that  $R_1=130~\mathrm{k}\Omega,~R_2=150~\mathrm{k}\Omega,~R_E=7.5~\mathrm{k}\Omega,~\mathrm{and}~\beta=100,$  calculate

- (i) the working point  $(I_B, I_C \text{ and } V_{CE})$ , [6]

- (ii) input resistance  $R_{in}$ .

Hint:  $R_{in} \approx R_P(\beta R_E + r_{be})/[R_P + \beta R_E + r_{be}]$ .

[4]

**END**