#### UNIVERSITY OF SWAZILAND

### **FACULTY OF SCIENCE**

### DEPARTMENT OF PHYSICS

MAIN EXAMINATION

2008/2009

TITLE OF PAPER:

DIGITAL ELECTRONICS

COURSE NUMBER

P411

TIME ALLOWED:

3 HOURS

**INSTRUCTIONS:**

ANSWER ALL QUESTIONS.

EACH QUESTION CARRIES 20 MARKS.

MARKS FOR DIFFERENT SECTION ARE SHOWN ENCLOSED IN SQUARE BRACKETS.

THIS PAPER HAS 5 PAGES INCLUDING THIS PAGE.

DO NOT OPEN THE PAPER UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR.

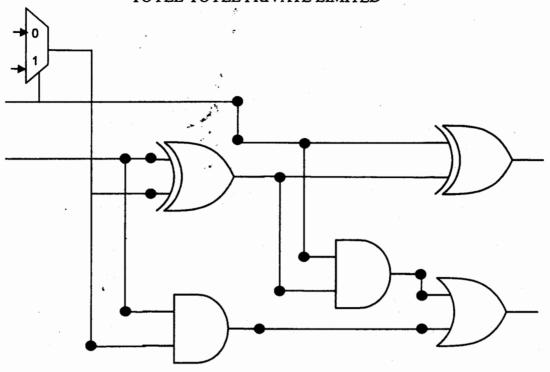

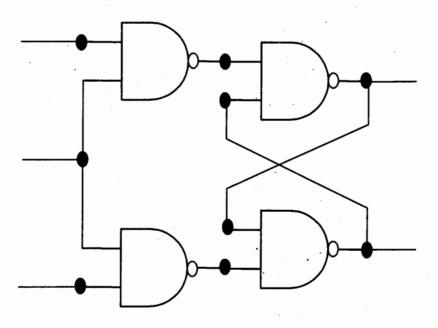

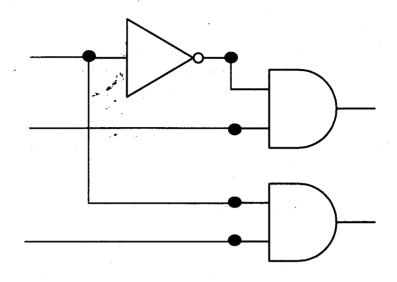

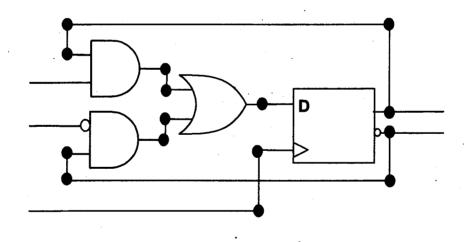

State De Morgan's theorems. [4] 1 (a) Simplify the following expressions using Boolean algebra: **(b)** (i)  $F = (X + \overline{Y} + \overline{X} \cdot Y) \cdot \overline{Z}$ [2] (ii)  $F = \overline{X} \cdot Y \cdot (X + \overline{Y} + \overline{X} \cdot Y)(X + \overline{Y})$ [2] (c) Given that:  $F = W \cdot X \cdot \overline{Y} \cdot Z + W \cdot \overline{X} \cdot \overline{Y} \cdot \overline{Z} + \overline{X} \cdot Y + \overline{W} \cdot \overline{X} + \overline{W} \cdot X \cdot \overline{Y} \cdot Z$ (i) [7] Use a Karnaugh Map to simplify F. (ii) Draw the logic circuit using only NAND gates for the simplified F expression. [2] (iii) Identify any static hazards and show how the hazards can be eliminated using a K-Map. [1] (iv) Following from (iii), draw the logic circuit but using only 2-[2] input NAND gates. 2 (a) Toyee-Toyee Private Limited, a local company engaged in reverse [5 each] engineering of electronic toys has sent you 4 logic circuit diagrams in Appendix A. Name each circuit (e.g. D-type Flip-Flop), label the inputs and outputs (e.g. A,B,C data input), and determine the truth table. 3 (a) In the context of digital electronics, explain the terms: (i) Register [2] (ii) Counter [2] (b) Design a 4-bit upward counting ripple counter using negative (i) edge-triggered JK flip-flops. [10](ii) Explain using at most 100 words how your design in 3b(i) operates. [4] (iii) Explain in not more than 50 words what modifications to your design in 3b(i) would produce a 4-bit downward ripple counter. [4] (a) Write down the equation form for the binary to gray code conversion rule. [2]

|   | (D)                                                                                                                                        | Convert the following into Gray-code.                  |                                                                                                                                   |              |

|---|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|

|   |                                                                                                                                            | (i)                                                    | DE <sub>16</sub>                                                                                                                  | [2]          |

|   |                                                                                                                                            | (ii)                                                   | 7148                                                                                                                              | [2]          |

|   |                                                                                                                                            | (iii)                                                  | 10000011 <sub>BCD</sub>                                                                                                           | [3]          |

|   | (c)                                                                                                                                        | Confirm with a truth table if TRUE or FALSE that:      |                                                                                                                                   |              |

|   |                                                                                                                                            | (i) NANE                                               | ) function is associative.                                                                                                        | [3]          |

|   |                                                                                                                                            | (ii) XNOI                                              | R function is not associative.                                                                                                    | [3]          |

|   | (d)                                                                                                                                        | Design a 3 bit full adder using a 3-to-8 line decoder. |                                                                                                                                   |              |

| 5 | 5 (a) Write brief notes that also include truth tables, function table logic circuit diagrams, or Boolean expressions on any 2 of the form |                                                        | ef notes that also include truth tables, function tables, K-Maps, uit diagrams, or Boolean expressions on any 2 of the following: | [10<br>each] |

|   |                                                                                                                                            | (i)                                                    | Prime Implicant, Essential Prime Implicant, Distinguished 1-Cell.                                                                 |              |

|   |                                                                                                                                            | (ii)                                                   | Edge-triggered and clocked flip-flop.                                                                                             |              |

|   |                                                                                                                                            | (iii)                                                  | Combinational Logic and Sequential Logic Circuits                                                                                 |              |

|   |                                                                                                                                            |                                                        |                                                                                                                                   |              |

## APPENDIX A - DATASHEET

## TOYEE-TOYEE PRIVATE LIMITED

# LOGIC CIRCUIT 1

**LOGIC CIRCUIT 2**

**LOGIC CIRCUIT 3**

**LOGIC CIRCUIT 4**