## UNIVERSITY OF SWAZILAND

# FACULTY OF SCIENCE DEPARTMENT OF PHYSICS

# 2006/2007 SUPPLEMENTARY EXAMINATION

Title of the Paper: **DIGITAL ELECTRONICS**Course Number: **P411**Time Allowed: **Three Hours**.

#### Instructions:

- 1. To answer, pick any five out of six questions in the following pages.

- 2. Each question carriers 20 points.

- 3. This paper has 7 pages, including this page.

DO NOT OPEN THE PAPER UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR.

### **QUESTION 1**:

a: Transform the K-Map below into

(10 marks)

- (1). a Truth Table,

- (2). a function in the following format (a SOP):  $F_1(B, C, D, E) = \sum (n1, n2, ---, nB, nC, ---, nF)_{hex}$

- (3). a function in the following format (a POS):  $F_2(B, C, D, E) = \prod (n1, n2, ---, nB, nC, ---, nF)_{hex}$  The number in the above brackets must be hexadecimal.

**b:** Prove  $F_1 = F_2$ . (must have equations to support)

(10 marks)

| DE |    |    |    |    |

|----|----|----|----|----|

| BC | 00 | 01 | 11 | 10 |

| 00 | 1  | 1  |    | 1  |

| 01 |    | 1  | 1  |    |

| 11 |    | 1  |    |    |

| 10 | 1  | 1  |    | 1  |

### **QUESTION 2**:

Using the tabulation method, simplify the following Boolean function F into an SOP:

$F(v, w, x, y, z) = \sum (0, 4, 9, B, D, F, 12, 13, 16, 17, 19, 1B, 1D, 1F)_{hex}$  (hex number in the brackets of the above function) (20 marks)

## **QUESTION 3:**

a: With the help of a K-map, obtain the simplified expression of the Boolean Function below in both SOP and POS. (10 marks)

$$F(A,B,C,D,) = \overline{A}(\overline{BD} + CD + BC)$$

$$d(A,B,C,D) = A(CD + \overline{BD}) + \overline{A}B\overline{C}D$$

b: Implement the Boolean function,

$$F(A,B,C,D,E) = (ACD + E)(A + \overline{B}) + BC\overline{D}E$$

,

with only NOR gates and nothing but NOR gates. Complement inputs are available only at input terminals, nowhere else. The implement must have its function support. (10 marks)

ŝ

#### **QUESTION 4:**

a: Implement the following function with a multiplexer of 4-1 (must have this component) and other elementary gates. Assign xy as the address of the MUX. (10 marks)

$$F(v, w, x, y) = \sum (1, 3, 7, 8, 9, A, D, F)_{hex}$$

(hex number in the brackets of the above function)

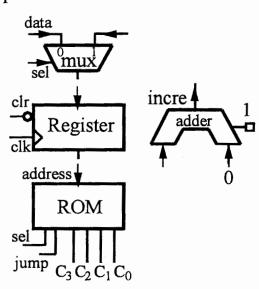

**b:** In the figure below is a micro-programmed sequencer (the circuit is not complete yet). In the ROM, there are fields in a byte: jumping address, mux select address, and sequence output, C. First, complete the circuit wiring to make the sequencer have a proper function as listed in the ROM table. Next, fine the sequence C that the processor runs through; the sequencer starts at address 0000 and finally jumps back to 0000.

|                                 |              |               | (10 marks)       |  |

|---------------------------------|--------------|---------------|------------------|--|

| ROM                             | ROM contents |               |                  |  |

| addr                            | sel          | jump          | С                |  |

| 0                               | 1            | x             | A                |  |

| 1                               | 1            | x             | 2                |  |

| 2                               | 0            | A             | 4                |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 1            | x             | A 2 4 7 C F      |  |

| 4                               | 1            | x             | C                |  |

| 5                               | 1            | x             | F                |  |

| 6                               | 1            | x             | 9                |  |

| 7                               | 0            | <b>x</b><br>0 | 4                |  |

| 8                               | 1            | x             | 1                |  |

| 8                               | 1            | x             | 3                |  |

| A<br>B<br>C<br>D                | 0            | Е             | 1<br>3<br>E<br>5 |  |

| В                               | 1 👞          | x             | 5                |  |

| C                               | 1            | x             | D                |  |

| D                               | 1            | x             | 0                |  |

| E                               | 0            | 6             | 0                |  |

| F                               | 0            | 0             | 6                |  |

### **QUESTION 5**:

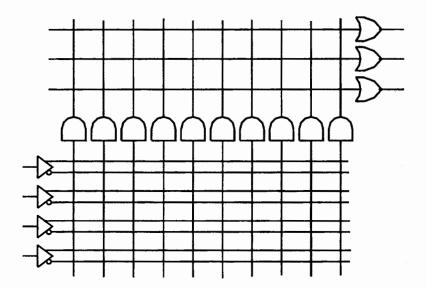

Design a sorting circuit for two 2-bit codes,  $B_1B_0$  and  $A_1A_0$ . Compare two codes to find out "B>A"; ie, F=1, when B>A. Design the circuit to fit in a PLA. Simplification is required. The circuit must have its function support. (hint, using logical inference, or an abridged truth table. A simplification identity  $(X + \overline{X}Y) = X + Y$ ). (20 marks)

### **QUESTION 6**:

Design, with D-ff's, a clocked sequencer to cycle repeatedly through the states: - - 0, 1, 3, 7, 5, 2, - - -. Not-used states must be properly treated. Obtain a state diagram, a state table, ff input functions, and finally a logic circuit. Does this sequencer need a hidden unit? (20 marks)